### A "Reverse-Feeding" Hold-up Time Strategy for Two-Stage Grid-Interface PFC with a Rectifier-Coupled Boost Inductor

Jaeil Baek<sup>1</sup>, Gun-Woo Moon<sup>2</sup>, and Minjie Chen<sup>1</sup>

<sup>1</sup>Princeton University, <sup>2</sup>KAIST

Note: This work was started at KAIST and completed at Princeton University

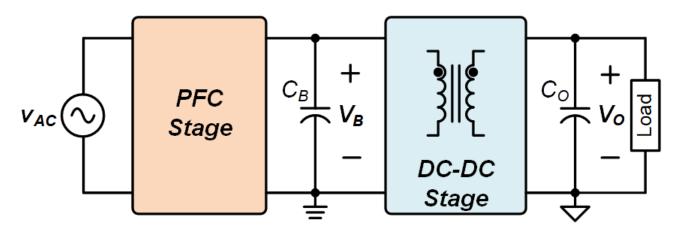

### **Two-stage grid-interface PFC architecture**

#### Needed in a wide range of applications

• Data-center / Transportation / Industrial applications

[Two-stage grid-interface PFC]

#### Design targets

- High efficiency / high power density

- High power quality

- Hold-up time requirement

- PFC stage

→ High power quality,  $V_B$  regulation

- DC/DC stage

- → Isolation,  $V_o$  regulation

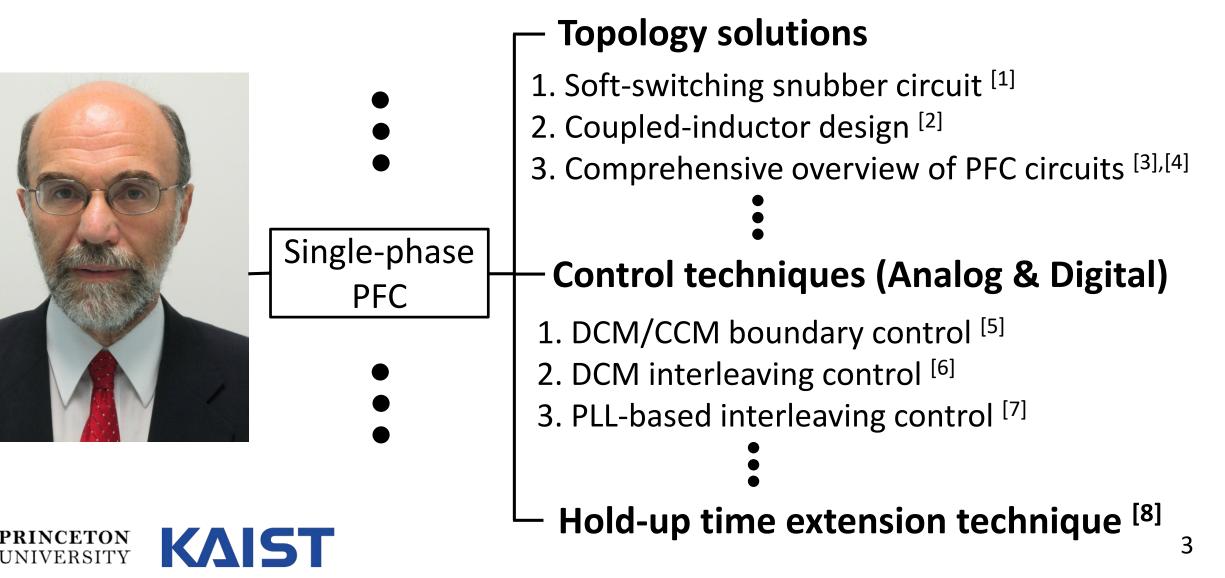

## **Dr. Jovanovic's contribution to PFC applications**

#### A wide range of contribution to power electronics field

#### Hold-up time requirement in PFC

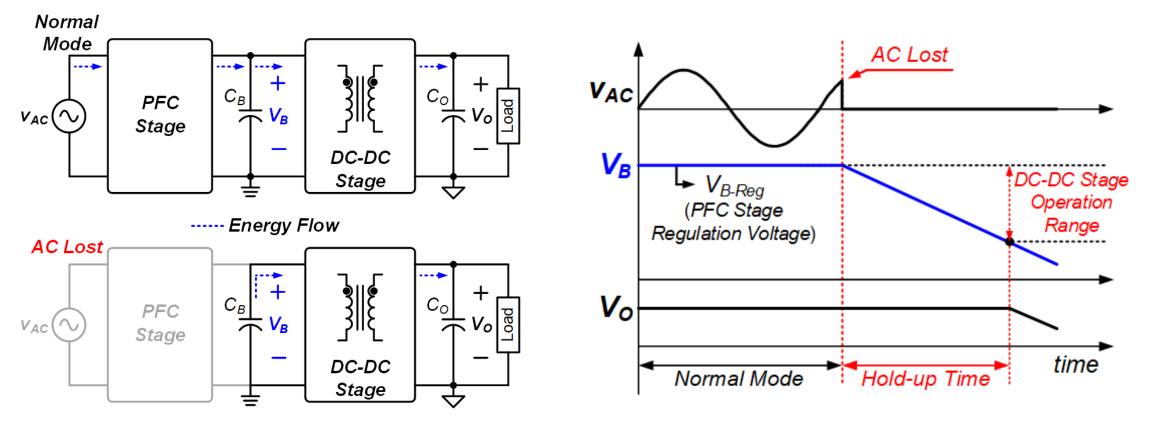

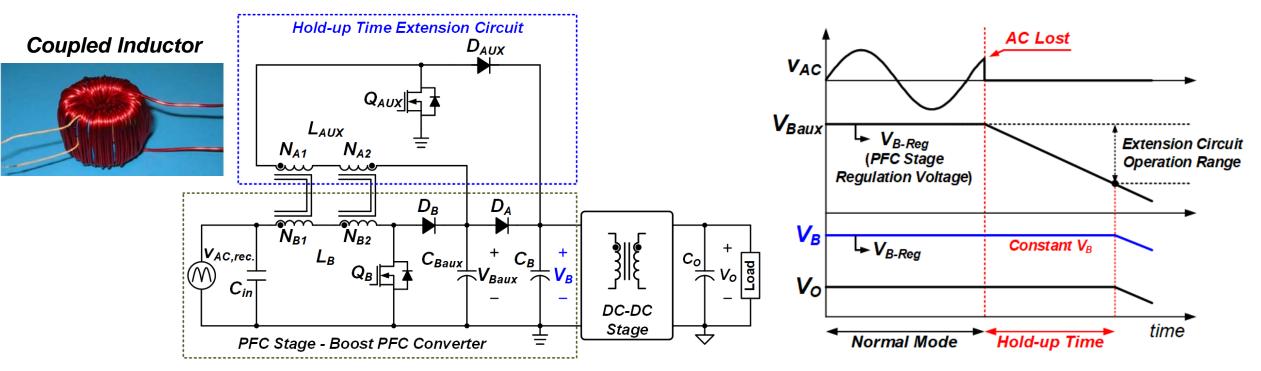

[Operations and waveforms of PFC during hold-up time]

• The HUT requirement set the limit for efficiency & energy buffer capacitor size

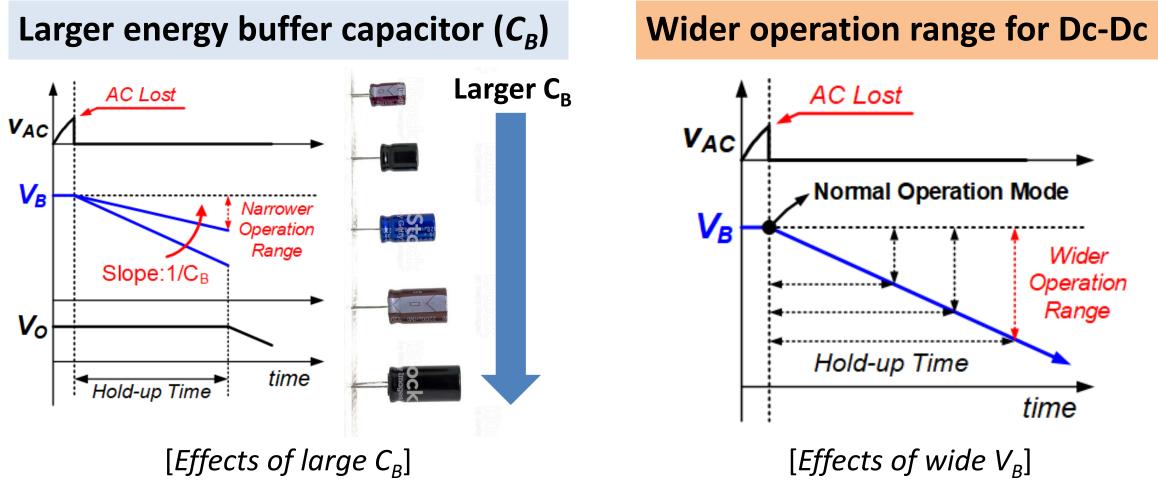

### Methods for extending the hold-up time

• Larger  $C_B \rightarrow$  Lower power density

RINCETON

UNIVERSITY

#### • Wider range → Lower peak efficiency

### Dr. Jovanovic's hold-up time contribution

#### **Hold-up Time Extension Circuit**

RINCETON

NIVERSITY

[Dr. Jovanovic's hold-up time compensation circuit [8]]

- Use a HUT extension circuit to reduce the dc-dc operation range

- Loss of D<sub>A</sub> in normal mode, large size of hold-up time extension circuit

### **Reverse-feeding strategy for two-stage PFC**

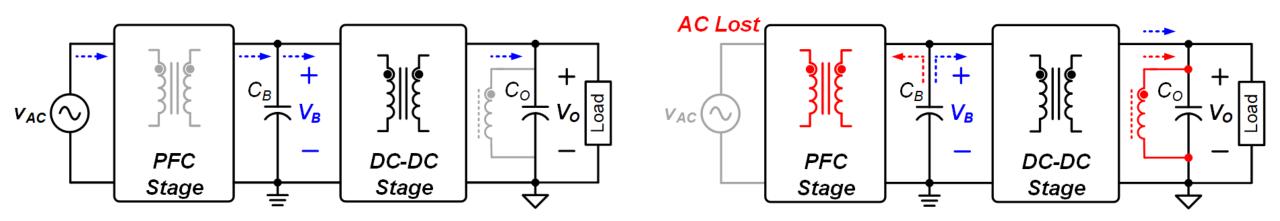

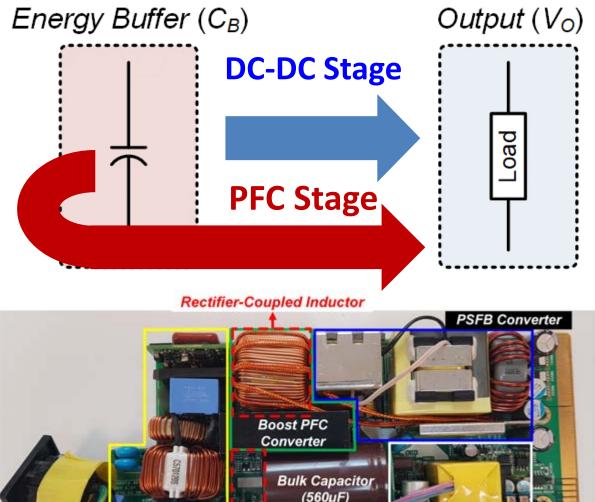

#### **Conventional strategy Reverse-feeding strategy** Energy Buffer ( $C_B$ ) Output $(V_0)$ Energy Buffer ( $C_B$ ) Output $(V_0)$ **DC-DC Stage DC-DC Stage** oad oad **PFC Stage** (Inactive) **PFC Stage** • Two-way feedings • Forward feeding

:  $C_B \rightarrow$  DC-DC Stage  $\rightarrow V_O$

ΚΔΙ

INCETON

NIVERSITY

- Forward:  $C_B \rightarrow$  DC-DC Stage  $\rightarrow V_O$

- **Reverse**:  $C_B \rightarrow PFC$  Stage  $\rightarrow V_O$

## Advantages of reverse-feeding strategy

#### Normal mode operation

Hold-up time operation

- 1. Reusing the inactivated PFC stage → Extended hold-up time

- 2. Easier DC/DC stage design like DCX transformer

#### → Improved peak efficiency in normal mode

3. Wider operation range → Reduced buffer capacitor size

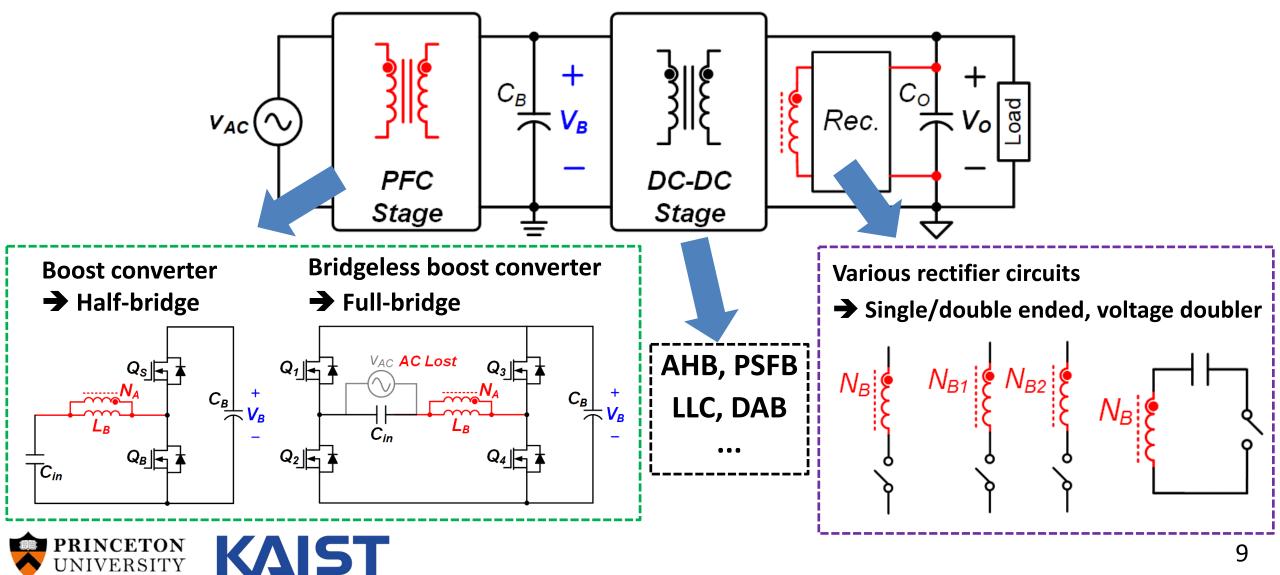

#### **Embodiments of reverse-feeding strategy**

#### Applicable to a variety of PFC & DC/DC topologies

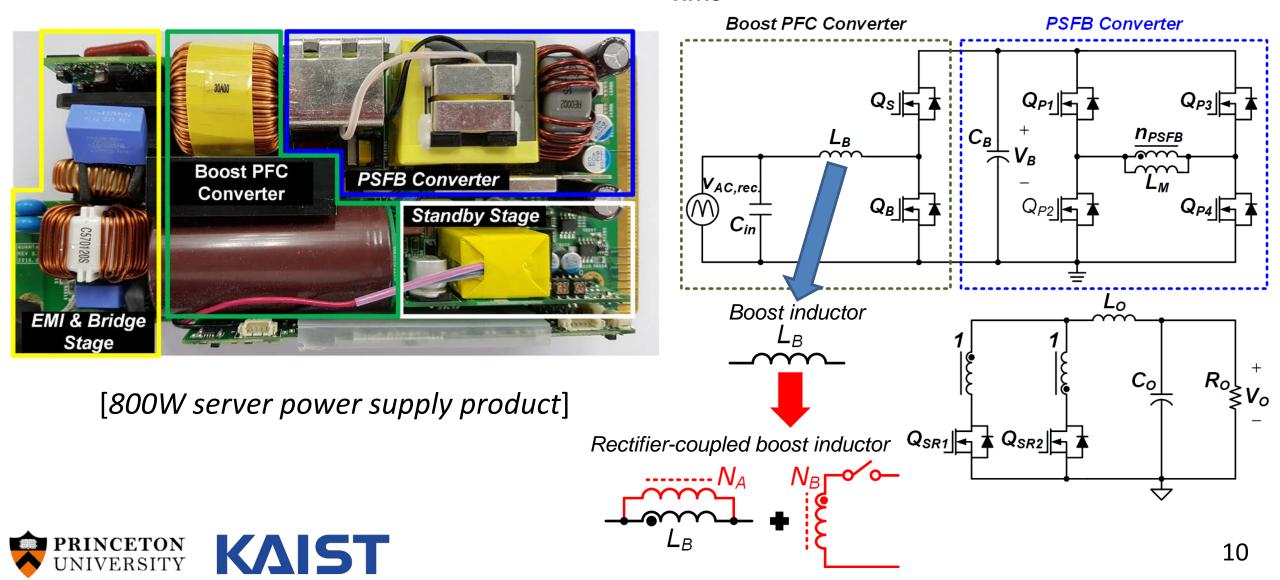

#### **Design example of a reverse-feeding PFC**

#### 800W server power supply (100-240V<sub>RMS</sub>, 12V/66.7A)

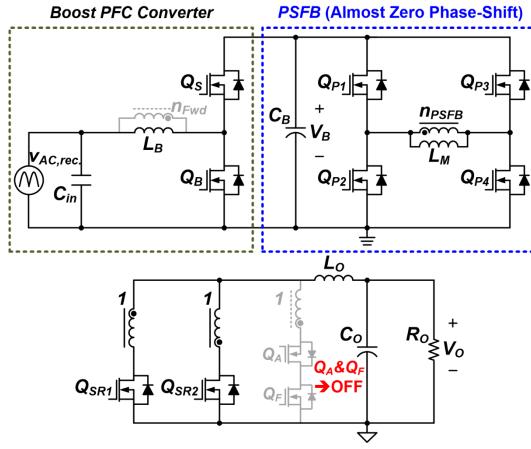

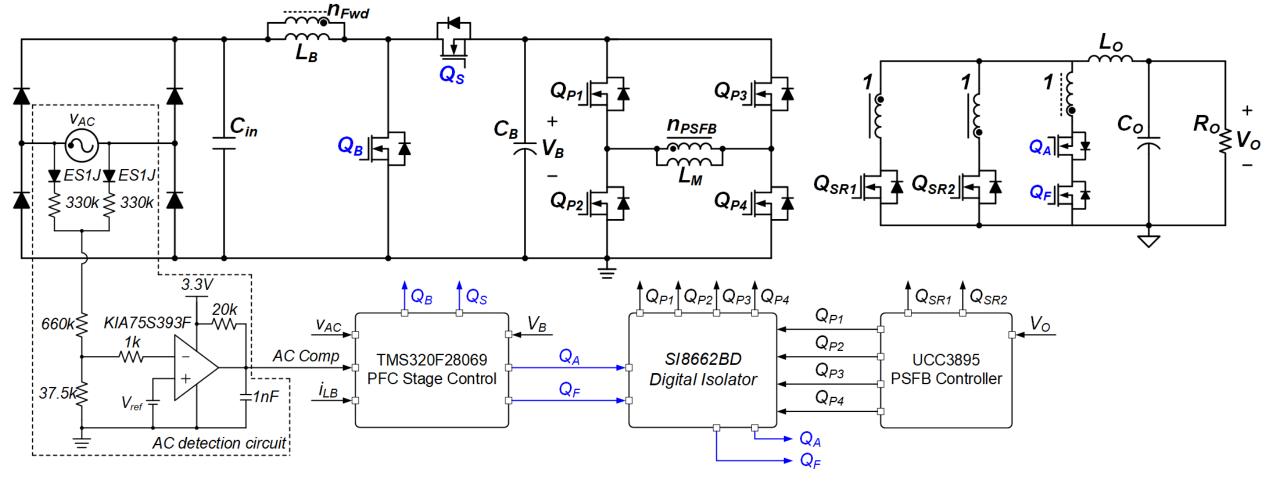

#### **Operational circuits – Two operation modes**

#### **Normal operation**

• Normal mode  $\rightarrow Q_A \& Q_F \text{ OFF}$

K

PRINCETON

UNIVERSITY

• Boost PFC + PSFB  $\rightarrow V_o$  regulation

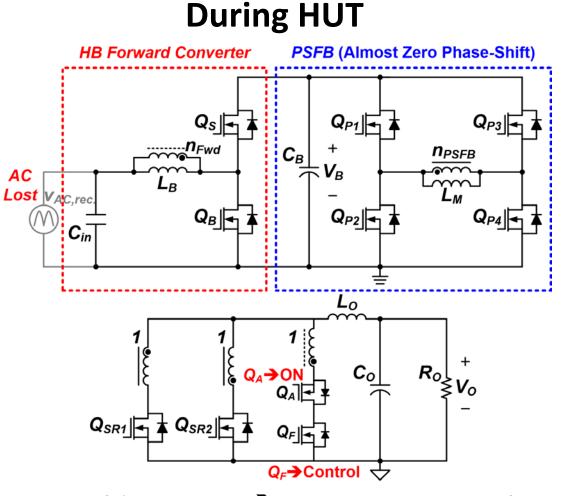

- Hold-up time  $\rightarrow Q_A \text{ ON}, Q_F \text{ control}$

- PSFB + HB forward  $\rightarrow V_o$  regulation

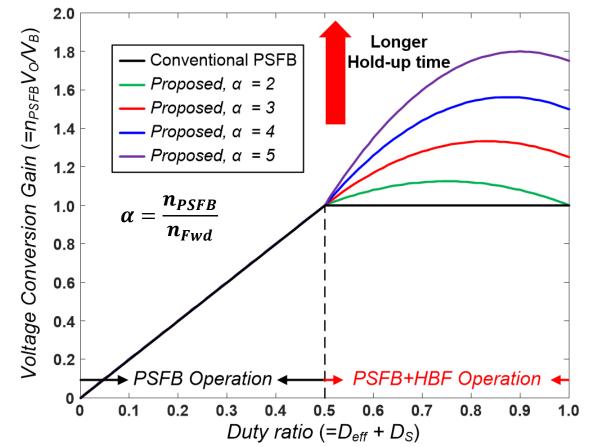

### Longer hold-up time & Higher efficiency

- Additional voltage gain of reverse feeding

- → Longer hold-up time

RINCETON

UNIVERSITY

➔ Narrower operation range design of PSFB

- Narrow operation range design of PSFB

- → Lower primary conduction loss

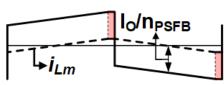

Wide V<sub>B</sub> Range Design Narrow V<sub>B</sub> Range Design

Freewheeling Current

V<sub>B</sub> : Input voltage of PSFB

➔ Lower output inductor core loss

(0.5-D<sub>eff</sub>)

V<sub>B</sub>/n<sub>PSFB</sub>

→ Lower snubber loss

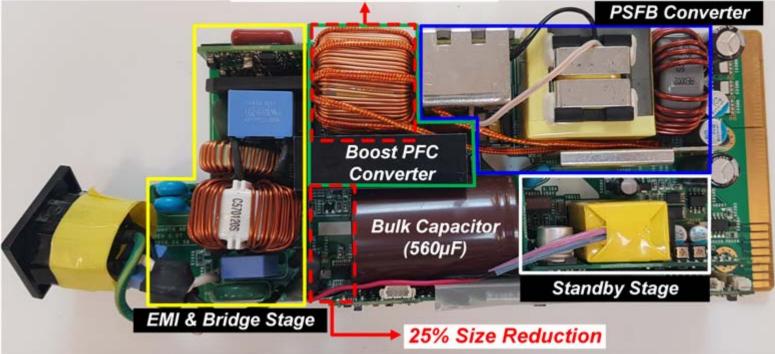

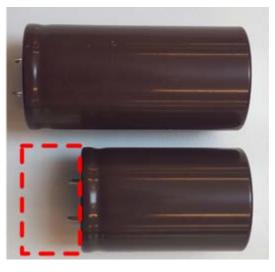

#### **Modified 800W server power supply prototype**

# IEEE ENERGY CONVERSION CONGRESS & EXPO

#### **Rectifier-Coupled Inductor**

• Same size of rectifier-coupled boost inductor

KAIST

PRINCETON

UNIVERSITY

- Smaller size of buffer capacitor (25% size reduction)

- Higher peak system efficiency in normal mode (95% -> 96%)

Conventional Inductor N<sub>A</sub>: 1.2Ф, 72 turns

Rectifier-Coupled Boost Inductor  $N_A$ : 1.1 $\Phi$ , 72 turns  $N_B$ : 0.05 $\Phi$ ×320, 8 turns

810µF (42.411cm<sup>3</sup>)

560μF (31.809cm<sup>3</sup>)

### **Control block diagram of prototype**

PRINCETON

UNIVERSITY

K

- 1. Conventional method :  $Q_B \& Q_S \rightarrow$  Always boost PFC operation

- 2. Reverse-feeding strategy :  $Q_B \& Q_S \Rightarrow$  Half-bridge forward operation (hold-up time)

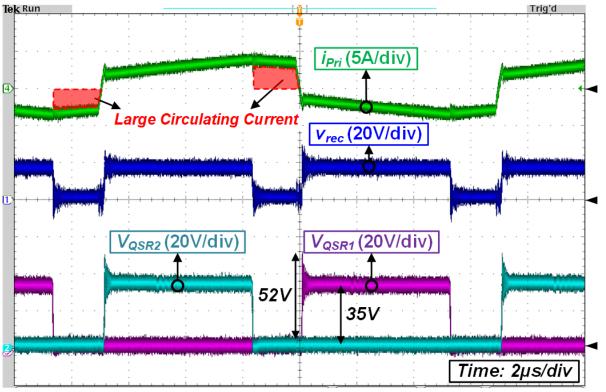

### Measured waveforms in normal mode

[Conventional PSFB converter]

- Wide operation range design (320V-400V)

- High circulating current

K

PRINCETON

UNIVERSITY

• High inductor core loss, High voltage stress

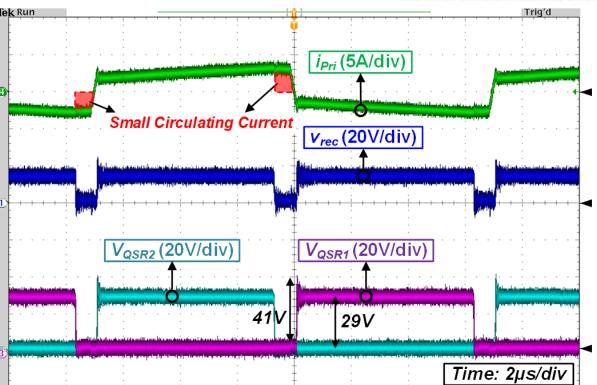

[PSFB converter with reverse-feeding]

- Narrow operation range design (380V-400V)

- Lower circulating current

- Lower core loss, Lower voltage stress

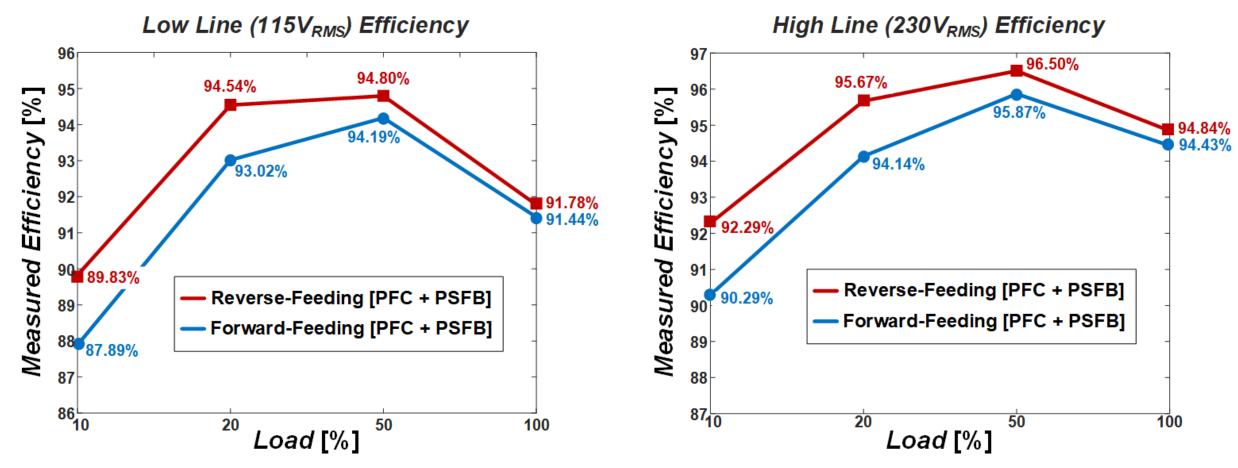

### System efficiency in normal mode

Peak efficiency : 94.8% @ 115V<sub>RMS</sub> (+0.59%), 96.5% @ 230V<sub>RMS</sub> (+0.63%)

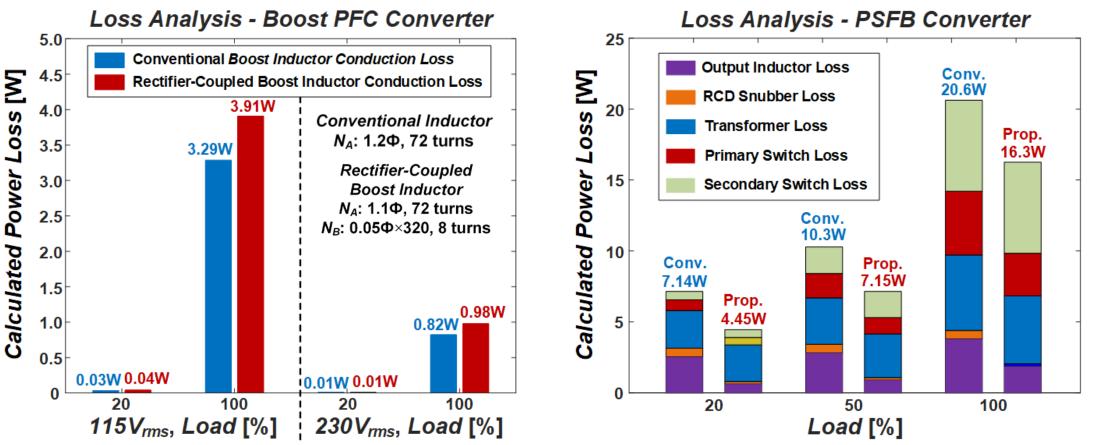

### Normal mode loss analysis

- Similar boost PFC converter efficiency, Higher efficiency PSFB converter

- Reverse-feeding → Higher system efficiency in universal line

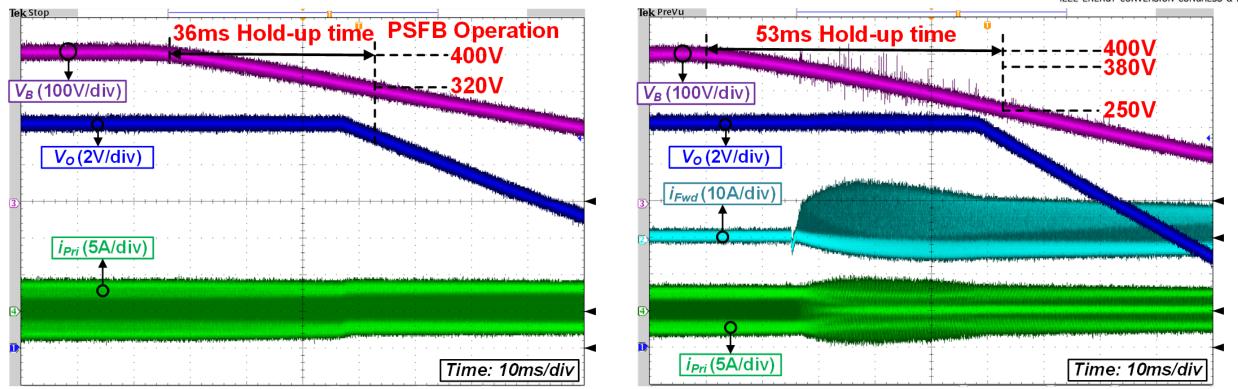

### **Measured hold-up time**

[Conventional PSFB converter, n<sub>PSFB</sub>=23:1]

KAIS

RINCETON

NIVERSITY

[PSFB converter with reverse-feeding, n<sub>PSFB</sub>=28:1]

- Conventional forward feeding: 400V-320V → PSFB operation (36ms hold-up time)

- Reverse feeding : (1) 400V-380V → PSFB, (2) 380V-250V → HB Forward + PSFB

(47% longer hold-up time with the same buffer capacitor)

#### Summary

- Reverse-feeding strategy for two-stage gridinterface PFC applications

- 1. Inactivated PFC stage → Reverse feeding

- 2. Easier DC/DC stage design (DCX transformer)

- 3. Wider operation range during hold-up time

- Applicable to a variety of PFC and DC/DC topologies

- Design example : 800W server power supply

- 96.5% (+0.63%) peak efficiency at 230V<sub>RMS</sub>

- 25% size reduction of buffer capacitor or 25% hold-up time extension

& Bridge Stage

19

Standby

25% Size Reduction

### References

- 1. Y. Jang, M. M. Jovanovic, K. H. Fan, and Y. M. Chang, "High-Power-Factor Soft-Switched Boost Converter," *IEEE Transactions on Power Electronics*, vol.21, no.1, pp. 98-104, January 2006.

- 2. Y. Jang and M. M. Jovanovic, "A Bridgeless PFC Boost Rectifier With Optimized Magnetic Utilization," *IEEE Transactions on Power Electronics*, vol.24, no.1, pp. 85-93, January 2009.

- 3. L. Huber, Y. Jang, and M. M. Jovanovic, "Performance Evaluation of Bridgeless PFC Boost Rectifier," *IEEE Transactions* on Power Electronics, vol.23, no.3, pp. 1381-1390, May 2008.

- 4. M. M. Jovanovic, Y. Jang, "State-of-the-Art, Single-Phase, Active Power-Factor-Correction Techniques for High-Power Applications-An Overview," *IEEE Transactions on Power Electronics*, vol.52, no.3, pp. 701-708, June 2005.

- L. Huber, B. T. Irving, M. M. Jovanovic, "Effect of Valley Switching and Switching-Frequency Limitation on Line-Current Distortions of DCM/CCM Boundary Boost PFC Converter," IEEE Transactions on Power Electronics, vol.24, no.2, pp. 339-347, February 2009.

- 6. J. Zhang, J. Shao, P. Xu, F. C. Lee, and M. M. Jovanovic, "Evaluation of Input Current in the Critical Mode Boost PFC Converter for Distributed Power Systems," *IEEE Applied Power Electronics Conference and Exposition (APEC), Anaheim, CA, 2001, pp. 130-136.*

- 7. L. Huber, B. T. Irving, and M. M. Jovanovic, "Review and Stability Analysis of PLL-Based Interleaving Control of DCM/CCM Boundary Boost PFC Converters," IEEE Transactions on Power Electronics, vol.24, no.8, pp. 1992-1999, August 2009.

- 8. Y. Jang, M. M. Jovanovic, and D. L. Dillman, "Hold-up Time Extension Circuit With Integrated Magnetics," IEEE Transactions on Power Electronics, vol.21, no.2, pp. 394-340, March 2006.